EPYC Rome (7002 series)

EPYC Rome

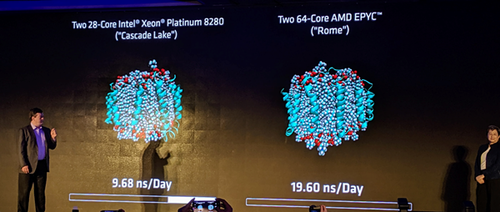

In brief - At Computex 2019, we had some fun controversy in the server space. During the AMD Keynote, AMD showed off the upcoming 64-core AMD EPYC “Rome” generation performance in NAMD versus dual 28-core Intel Xeon Platinum 8280 CPUs. After the keynote, Intel quickly followed with a response showing results with its Intel Xeon Platinum 9200 series. Second half of 2019 is going to be a lot of fun in the server space. HPCMATE with local and global partners are preparing HPC optimized AMD based GPGPU server in Q4’19.

Rome

Based on the 2019 Computex presentation, EPYC Rome is slightly later to server market (Q3’19) but is offering 55% more performance than Intel’s mainstream top-end part (Xeon Platinum 8280) that is shipping today. That is a massive improvement. Combine this with more memory channels, memory capacity, PCIe lanes, PCIe Gen4 bandwidth, and we are no longer in the realm of this being close given Intel’s Cascade Lake family.

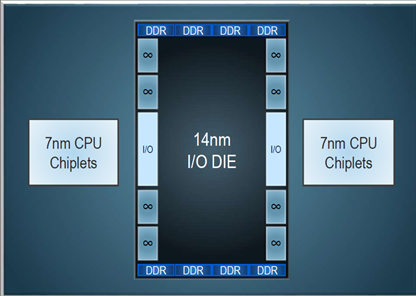

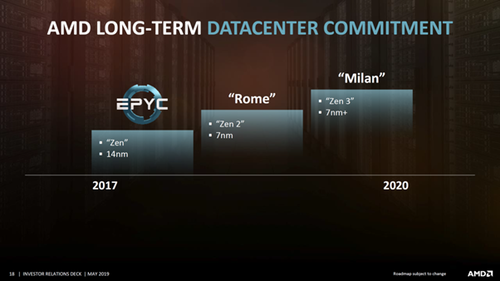

With EPYC Rome, AMD skipped 10nm and went straight for 7nm and EPYC Rome is the worlds first 7nm Datacenter CPU family with Significant IPC (instructions per clock) Gains. AMD confirmed that the EPYC Rome series server processors would make use of eight 7nm CPU chiplets which will be connected to a large separate 14nm I/O die that controls all of the memory, I/O and interconnects which the CPU dies can make direct access to. This separate die for I/O will enable faster memory and chip to chip access than before.

Key features

The CPU chiplets will be able to house up to 64 cores and 128 threads. The EPYC Rome processors will also have access to faster 8 channel DDR4 memory lanes, allowing for higher bandwidth. Rome SoCs support both single and 2-way multiprocessing with up to a maximum of 64 cores (and 128 threads) per processor for a total of up to 128 cores (and 256 threads) for a 2-way MP system. Those SoCs support 128 PCIe Gen 4 lanes each, however, half of them are lost when in 2-way MP (leaving the system with the same overall lanes count as a single socket solution). Communication between the two chips is done via AMD's Infinity Fabric protocol over the 64 reserved lanes. Rome is backwards platform/socket compatible with Naples and forward-compatible with Milan.

Rome will support 3200 MHz RAM in eight channels, for up to 4 TB of RAM per socket (While Intel is presently limited to 2 TB across six channels, and only up to speeds of 2666 MHz) PCIe 4.0 and 128 PCIe lanes Intel processors have significantly higher TDPs at the high-end, much higher prices at the low-end, and far less cache the whole way through

In summary, all Rome processors have the following:

- 128 PCIe lanes PCIe Gen 4 (in both single-way and dual-way multiprocessing)

- Octa-channel Memory

- Up to DDR4-3200 ECC 4 TiB (8 TiB in 2MP)

- Up to 64 cores / 128 threads

- Everything up to AVX2 (i.e., SMM, FPU, NX, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, AES, AVX, FMA3, and AVX2), and SHA

EPYC Rome series

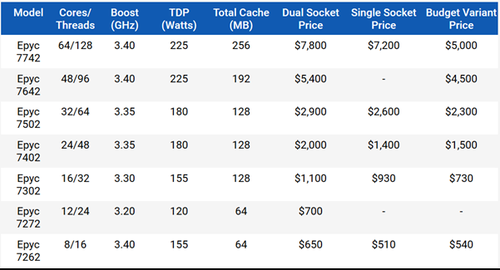

According to Techspot[1], AMD is bringing 64, 48, 32, 24, 16, 12 and 8 core variants to the market this time, most of which are available in three configuration options. A fancy-pants dual-socket compatible version, a single-socket version with identical specs (bar one or two exceptions) and a ‘budget’ variant that cuts back a little while increasing power efficiency

The AMD EPYC Rome processor family is expected to lift AMD’s server CPU market share to 10% by 2020. AMD’s 32-core processor is 29% cheaper than Intel’s 28-core, their 24-core part is 57% cheaper, and their 16-core part is 69% cheaper [2]

- Wccftech’s article shows EPYC Rome 7452 with 32 cores moninating position against Intel’s Xeon and much faster than EPY Naples [3]

- Dell EMC announced that they will be launching servers powered by AMD’s newest architecture – a 7nm architecture codenamed ‘Rome’ – in the second half of 2019 - Dominique Vanhamme (DELL EMEA vice president)

- Microsoft took the stage at its E3 2019 keynote, announcing that the system-on-a-chip powering the next Xbox, Project Scarlett, is using Zen 2 cores and AMD Navi graphics. Microsoft certainly is talking a deep partnership with AMD during computex. When talking about Windows, Roanne explicitly mentioned "mission critical system...and government" during Computex on stage, as well as "premium sector and next level".

Reference

- ↑ https://www.techspot.com/news/80631-amd-7nm-epyc-rome-specs-prices.html

- ↑ AMD 7nm Epyc Rome specs and prices leak

- ↑ EPYC Rome 7452 with 32 cores moninating position against Intel, url=https://wccftech.com/amd-epyc-7452-7nm-rome-server-cpu-benchmark-versus-intel-xeon/